#### DDR5 Client VR-on-DIMM PMIC

### **Description**

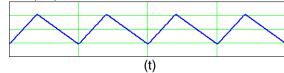

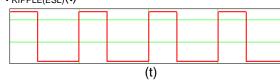

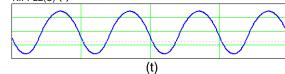

The FP9968 is an integrated solution for DDR5 SODIMM and UDIMM power management IC. The PMIC features three buck converters and two LDO regulators. The buck converters are designed by capacitor current sense constant on time (CCS COT) control that provides fast transient response, the noise immunity and all kinds of very low ESR output capacitor for ensuring performance stabilization. All three buck converters equip with automatic power saving mode (PSM) for optimizing efficiency. The two LDO regulators, VOUT\_1.0V and VOUT\_1.8V, can supply DIMM module's sideband and SDP usage. The PMIC supports selectable interface (I<sup>2</sup>C or I<sup>3</sup>C Basic) to fit various application environment.

Two of the buck converters (SWA and SWB) can be configured to operate in dual-phase single channel. Two ADCs are implemented to monitor the current consumptions of the buck converters and the voltage information of the input/output rails.

The FP9968 is available in low-profile thermal enhanced TQFN-28 (3mmx4mm) package.

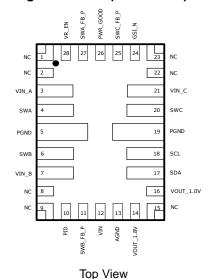

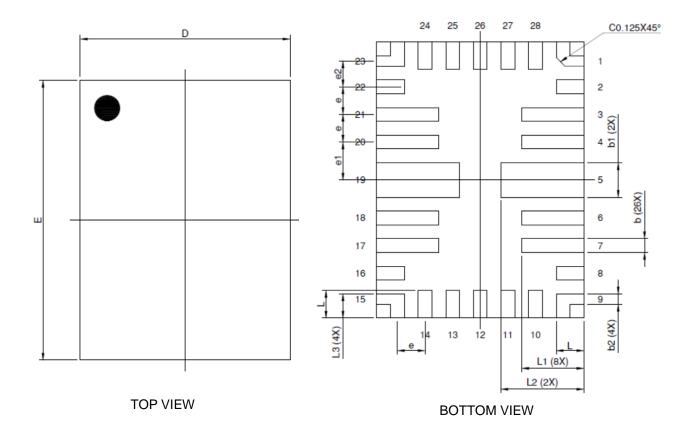

### **Pin Assignments**

J15 Package: TQFN-28 (3mmx4mm)

Figure 1. Pin Assignment of FP9968

#### **Features**

- VIN\_Bulk Input Supply Range: 4.25V to 5.5V

- Three Buck Converters: SWA, SWB & SWC

- Configurable Dual Phase and Single Phase Node for SWA and SWB

- 0.75% Output Accuracy

- Configurable Switching Frequency of Buck

- CCS COT Mode Enables Fast Transient Response

- 2 LDO Regulators: VOUT\_1.8V, VOUT\_1.0V

- Secure Mode and Programmable Mode of Operation

- Supports I<sup>2</sup>C and I<sup>3</sup>C Interface

- Controllable Soft-start /Soft-stop Time of Buck

- Protection Functions, Including OVP, UVP, OCP and OTP

- Power Good Indicator

- General Status Interrupt Function

- TQFN-28 (3mmx4mm) Package

- RoHS Compliant

## **Applications**

• DDR5 SODIMM, UDIMM

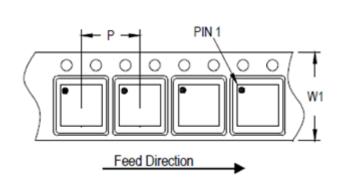

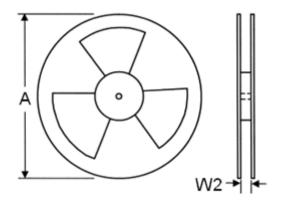

## Ordering Information

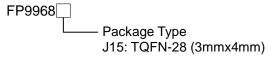

# **Typical Application Circuit**

Figure 2. SWA and SWB are operating in Single-Phase Mode

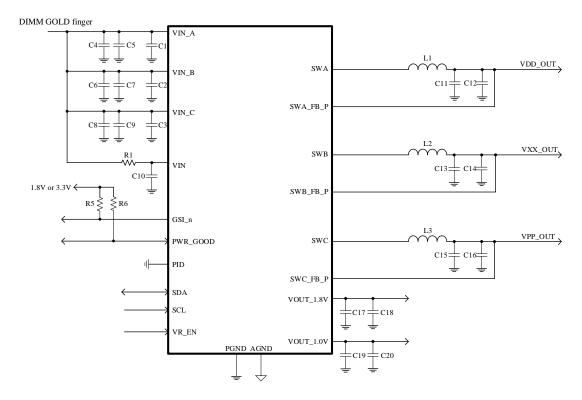

# **Typical Application Circuit (Continued)**

Figure 3. SWA and SWB are operating in Dual-Phase Mode

## **Functional Pin Description**

| Pin No.      | Pin Name                  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 15, 23 | NC                        | Non-functional pins. No internal connections to the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2, 8, 22     | NC                        | Non-functional pins. The pins must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3, 7, 21     | VIN_ A<br>VIN_ B<br>VIN_C | 5V power input supply to the PMIC for SWA, SWB and SWC respectively. All three VIN_Bulk input pins must be connected to the 5 V input supply even if one or more output regulators are not intended to be used.                                                                                                                                                                                                                                                                                                                                                                                               |

| 4            | SWA                       | Switch node A output buck regulator. This pin connects to L1 power inductor.  In single phase regulator mode of operation, the SWA output must not be connected to SWB output even if they are configured to same exact output voltage.  In dual phase regulator mode of operation, the SWA and SWB outputs are connected.                                                                                                                                                                                                                                                                                    |

| 5,19         | PGND                      | Power Ground. Connect PGND to DIMM ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6            | SWB                       | Switch node B output buck regulator. This pin connects to L2 power inductor. In single phase regulator mode of operation, the SWB output must not be connected to SWA output even if they are configured to same exact output voltage. In dual phase regulator mode of operation, the SWA and SWB outputs are connected.                                                                                                                                                                                                                                                                                      |

| 10           | PID                       | PMIC ID pin for I <sup>2</sup> C and I <sup>3</sup> C Basic bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11           | SWB_FB_P                  | Switch node B output buck regulator positive feedback. In single phase regulator mode of operation, this pin connects to DIMM power plane load. In dual phase regulator mode of operation, this pin is connected to GND.                                                                                                                                                                                                                                                                                                                                                                                      |

| 12           | VIN                       | 5 V power input supply to the PMIC for analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13           | AGND                      | Analog Ground. Connect AGND to DIMM ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14           | VOUT_1.8V                 | 1.8V LDO Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16           | VOUT_1.0V                 | 1.0V LDO Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17           | SDA                       | Data input and output for I <sup>2</sup> C and I <sup>3</sup> C Basic bus management interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18           | SCL                       | Clock input for I <sup>2</sup> C and I <sup>3</sup> C Basic bus management interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20           | swc                       | Switch node C output buck regulator. This pin connects to L3 power inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24           | GSI_n                     | General Status Interrupt. Open Drain Output. This PMIC asserts this pin low to communicate any or more events to host. This pin stays asserted until the appropriate registers are explicitly cleared and event is no longer present.                                                                                                                                                                                                                                                                                                                                                                         |

| 25           | SWC_FB_P                  | Switch node C output buck regulator positive feedback. This pin connects to DIMM power plane load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26           | PWR_GOOD                  | Power good indicator. Open Drain output. The PMIC floats this pin high when VIN_Bulk input supply as well as all enabled output buck regulators and all LDO regulator tolerance threshold is maintained as configured in appropriate register. The PMIC drives this pin low when VIN_Bulk input goes below the threshold or when any of the enabled switch output regulators exceeds the threshold configured in the appropriate register or any LDO output regulator exceeds the threshold tolerance.  Input: The PMIC disables its output regulators when this pin is low. The LDO outputs shall remain on. |

| 27           | SWA_FB_P                  | Switch node A output buck regulator positive feedback. In single phase or dual phase regulator mode of operation, this pin connects to DIMM power plane load.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 28           | VR_EN                     | PMIC Enable. When this pin is high, the PMIC turns on the regulator. When this pin is low, the PMIC turns off the regulator. This pin shall not be left floating. If it is not used, it shall be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                 |

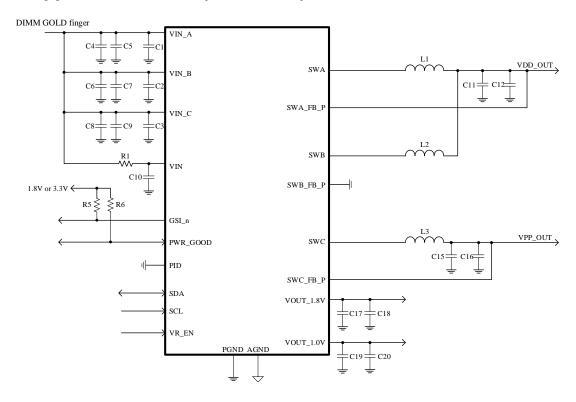

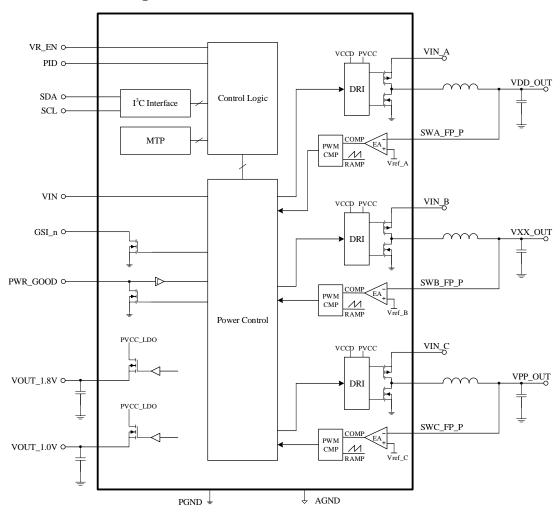

## **Functional Block Diagram**

Figure 4. Block Diagram of FP9968

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, VINA, VINB, VINC                                                        | -0.3V to +6V     |

|-------------------------------------------------------------------------------------------------|------------------|

| Supply Input Voltage, VIN                                                                       | -0.3V to +6V     |

| • AGND to PGND                                                                                  | -0.3V to +0.3V   |

| • Switching PIN, SWA, SWB, SWC                                                                  |                  |

| DC                                                                                              | -0.3V to +6V     |

| < 25ns                                                                                          | -0.3V to +9V     |

| • Other I/O                                                                                     | -0.3V to +6V     |

| • Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C                                     |                  |

| TQFN-28 (3mmx4mm)                                                                               | TBD              |

| Package Thermal Resistance                                                                      |                  |

| TQFN-28 (3mmx4mm), $\theta_{JA}$                                                                | TBD              |

| TQFN-28 (3mmx4mm), $\theta_{Jc}$                                                                | TBD              |

| • Junction Temperature                                                                          | -40°C to +155°C  |

| Storage Temperature Range                                                                       | -55°C to +150°C  |

| • Lead Temperature (Soldering, 10sec)                                                           | +260°C           |

| • ESD Susceptibility                                                                            |                  |

| HBM (Human Body Mode)                                                                           | +2KV             |

| CDM (Charged Device Mode)                                                                       | +500V            |

| Note 1: Stresses beyond this listed under "Absolute Maximum Ratings" may cause permanent damage | e to the device. |

## **Recommended Operating Conditions**

| • Supply Input Voltage, V <sub>INA</sub> , V <sub>INB</sub> , V <sub>INC</sub> | +4.25V to +5.5V |

|--------------------------------------------------------------------------------|-----------------|

| • Supply Input Voltage, V <sub>IN</sub>                                        | +4.25V to +5.5V |

| Junction Temperature Range                                                     | -10°C to +105°C |

| Ambient Temperature Range                                                      | 0°C to +85°C    |

### **Electrical Characteristics**

Limits apply over the full operating ambient temperature range (0°C  $\leq$  TA  $\leq$  85°C) and  $V_{INA} = V_{INB} = V_{INC} = V_{IN} = 5V$ , typical values are at  $T_A = 25$ °C, unless otherwise specified.)

| Parameter                                | Symbol                                                   | Conditions                                            | Min   | Тур   | Max   | Unit  |  |

|------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|-------|-------|-------|-------|--|

| Input Power Supply                       |                                                          |                                                       |       |       | •     |       |  |

| Input Supply Voltage DC Voltage          | V <sub>IN</sub>                                          |                                                       | 4.25  | 5     | 5.5   | V     |  |

| Input supply Voltage<br>VINA, VINB, VINC | V <sub>INA</sub> ,<br>V <sub>INB</sub> ,V <sub>INC</sub> | V <sub>IN</sub> Rising                                | 4.25  | 5     | 5.5   | V     |  |

| VIN Supply Current                       | I <sub>Q_VIN</sub>                                       | VR_EN=0; all LDO,SWA to SWC off, T <sub>A</sub> =25°C |       |       | 25    | μΑ    |  |

| SWA / SWB                                |                                                          |                                                       |       |       |       |       |  |

| Output Voltage Setting                   | V <sub>OUT_SWA/B</sub>                                   | Setting by reg_0x21[7:1] / 0x25[7:1]                  | 0.8   | 1.1   | 1.435 | V     |  |

| Output Voltage Accuracy                  | V <sub>OUT_SWA/B</sub>                                   | V <sub>BAT</sub> =5V only, lout=0,<br>CCM             | -0.75 |       | 0.75  | %     |  |

| Dynamic Voltage Scale slew rate          |                                                          |                                                       |       | 1     |       | mV/µs |  |

| Soft-start Time                          |                                                          | t <sub>set</sub> = 1ms to 14 ms                       | -15   |       | 15    | %     |  |

| Soft-stop Time                           |                                                          | t <sub>set</sub> = 0.5ms to 4 ms                      | -20   |       | 20    | %     |  |

| High side MOSFET R <sub>DS(ON)</sub>     | R <sub>DS(ON)</sub> _<br>swa/swb_h                       |                                                       |       | 25    |       | mΩ    |  |

| Low side MOSFET R <sub>DS(ON)</sub>      | R <sub>DS(ON)</sub> _<br>swa/swb_L                       |                                                       |       | 9.7   |       | mΩ    |  |

|                                          |                                                          | Setting by reg_0x29[5:4] / 0x2A[5:4]=00 (default)     | -15%  | 0.75  | +15%  | - MHz |  |

| Outtable a Francisco                     | f <sub>SW_SWA/B</sub>                                    | Setting by reg_0x29[5:4]<br>/ 0x2A[5:4]=01            | -15%  | 1.0   | +15%  |       |  |

| Switching Frequency                      |                                                          | Setting by reg_0x29[5:4]<br>/ 0x2A[5:4]=10            | -15%  | 1.25  | +15%  |       |  |

|                                          |                                                          | Setting by reg_0x29[5:4] / 0x2A[5:4]=11               | -15%  | 1.5   | +15%  |       |  |

|                                          |                                                          | Setting by reg_0x22[5:4] / 0x26[5:4]=00               |       | 7.5   |       |       |  |

| OVD Three-bald                           |                                                          | Setting by reg_0x22[5:4] / 0x26[5:4]=01               |       | 10    |       | 0/    |  |

| OVP Threshold                            |                                                          | Setting by reg_0x22[5:4] / 0x26[5:4]=10 (default)     |       | 12.5  |       | %     |  |

|                                          |                                                          | Setting by reg_0x22[5:4] / 0x26[5:4]=11               |       | 5     |       |       |  |

| OVP Propagation Delay                    | t <sub>OVPDLY_SWA/B</sub>                                |                                                       |       | 5     |       | μs    |  |

|                                          |                                                          | Setting by reg_0x22[3:2] / 0x26[3:2]=00 (default)     |       | -10   |       |       |  |

| LIV/D Three hold                         |                                                          | Setting by reg_0x22[3:2] / 0x26[3:2]=01               |       | -12.5 |       | %     |  |

| UVP Threshold                            |                                                          | Setting by reg_0x22[3:2] / 0x26[3:2]=10               |       | -5    |       |       |  |

|                                          |                                                          | Setting by reg_0x22[3:2]<br>/ 0x26[3:2]=11            |       | -7.5  |       |       |  |

| UVP Propagation Delay                    | tuvpdly_swa/b                                            |                                                       |       | 5     |       | μs    |  |

## **Electrical Characteristics (Continued)**

Limits apply over the full operating ambient temperature range (0°C  $\leq$  TA  $\leq$  85°C) and  $V_{INA} = V_{INB} = V_{INC} = V_{IN} = 5V$ , typical values are at  $T_A$ =25°C, unless otherwise specified.)

| Parameter                            | Symbol                                                   | Conditions                                  | Min   | Тур   | Max   | Unit   |  |

|--------------------------------------|----------------------------------------------------------|---------------------------------------------|-------|-------|-------|--------|--|

|                                      | Valley current limited Setting by reg_0x20[7:6]/[3:2]=00 |                                             |       | 5.0   |       |        |  |

| Current Limit                        | I <sub>LIM_SWA/B</sub>                                   | Setting by reg_0x20[7:6]/[3:2]=01 (default) |       | 5.5   |       | A      |  |

|                                      |                                                          | Setting by reg_0x20[7:6]/[3:2]=10           |       | 6.0   |       |        |  |

| SWC                                  |                                                          |                                             |       |       |       |        |  |

| Output Voltage Setting               | V <sub>OUT_SWC</sub>                                     |                                             | 1.5   | 1.8   | 2.135 | V      |  |

| Output Voltage Accuracy              | V <sub>OUT_SWC</sub>                                     | lout=0, CCM                                 | -0.75 |       | 0.75  | %      |  |

| Dynamic Voltage Scale slew rate      |                                                          |                                             |       | 1     |       | mV/µs  |  |

| Soft-start Time                      |                                                          | t <sub>set</sub> = 1ms to 14 ms             | -15   |       | 15    | %      |  |

| Soft-stop Time                       |                                                          | t <sub>set</sub> = 0.5ms to 4 ms            | -20   |       | 20    | %      |  |

| High side MOSFET R <sub>DS(ON)</sub> | R <sub>DS(ON)_SWC_H</sub>                                |                                             |       | 77    |       | mΩ     |  |

| Low side MOSFET R <sub>DS(ON)</sub>  | R <sub>DS(ON)_SWC_L</sub>                                |                                             |       | 26    |       | mΩ     |  |

|                                      |                                                          | Setting by reg_0x2A[1:0]=00                 | -15%  | 0.75  | +15%  |        |  |

| Switching Frequency                  | f <sub>SW_SWC</sub>                                      | Setting by<br>reg_0x2A[1:0]=01<br>(default) | -15%  | 1.0   | +15%  | MHz    |  |

| Ownering Frequency                   |                                                          | Setting by reg_0x2A[1:0]=10                 | -15%  | 1.25  | +15%  | IVIIIZ |  |

|                                      |                                                          | Setting by reg_0x2A[1:0]=11                 | -15%  | 1.5   | +15%  |        |  |

|                                      |                                                          | Setting by reg_0x28[5:4]=00                 |       | 7.5   |       |        |  |

|                                      |                                                          | Setting by reg_0x28[5:4]=01                 |       | 10    |       |        |  |

| OVP Threshold                        |                                                          | Setting by reg_0x28[5:4]=10 (default)       |       | 12.5  |       | %      |  |

|                                      |                                                          | Setting by reg_0x28[5:4]=11                 |       | 5     |       |        |  |

| OVP Propagation Delay                | tovpdly_swc                                              | <u> </u>                                    |       | 5     |       | μs     |  |

|                                      |                                                          | Setting by reg_0x28[3:2]=00 (default)       |       | -10   |       |        |  |

| UVP Threshold                        |                                                          | Setting by reg_0x28[3:2]=01                 |       | -12.5 |       | -<br>% |  |

|                                      |                                                          | Setting by reg_0x28[3:2]=10                 |       | -5    |       |        |  |

|                                      |                                                          | Setting by reg_0x28[3:2]=11                 |       | -7.5  |       | =      |  |

| UVP Propagation Delay                | t <sub>UVPDLY_</sub> SWC                                 |                                             |       | 5     |       | μs     |  |

### **Electrical Characteristics (Continued)**

Limits apply over the full operating ambient temperature range (0°C  $\leq$  TA  $\leq$  85°C) and  $V_{INA} = V_{INB} = V_{INC} = V_{IN} = 5V$ , typical values are at  $T_A$ =25°C, unless otherwise specified.)

| values are at T <sub>A</sub> =25°C, unless othe  Parameter                                           | Symbol                   | Conditions                                               | Min   | Тур | Max   | Unit |

|------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------|-------|-----|-------|------|

|                                                                                                      | I <sub>LIM</sub> SWC LOW | Valley current limited<br>Setting by<br>reg_0x20[1:0]=00 |       | 1.5 |       |      |

| Current Limit  VLDO_1.8V(1.8V, IMAX=25mA)  Output Voltage  Current Limit  VLDO_1.0V(1.0V, IMAX=20mA) |                          | Setting by reg_0x20[1:0]=01                              |       | 2.0 |       |      |

|                                                                                                      | Current                  | Setting by reg_0x20[1:0]=10                              |       | 2.5 |       | Α    |

|                                                                                                      |                          | Setting by reg_0x20[1:0]=11 (default)                    |       | 3.0 |       |      |

| VLDO_1.8V(1.8V, IMAX=25mA)                                                                           |                          |                                                          |       |     |       |      |

|                                                                                                      |                          | Setting by reg_0x2B[7:6]=00                              |       | 1.7 |       |      |

| Output Voltage                                                                                       | VLDO_1.8V                | setting by<br>reg_0x2B[7:6]=01<br>(default)              | -2.0% | 1.8 | +2.0% | V    |

|                                                                                                      |                          | Setting by reg_0x2B[7:6]=10                              |       | 1.9 |       |      |

|                                                                                                      |                          | Setting by reg_0x2B[7:6]=11                              |       | 2.0 |       |      |

| Current Limit                                                                                        |                          |                                                          |       | 200 |       | mA   |

| VLDO_1.0V(1.0V, IMAX=20mA)                                                                           |                          |                                                          | •     |     |       |      |

|                                                                                                      |                          | Setting by reg_0x2B[2:1]=00                              |       | 0.9 | +2.0% | V    |

| Output Voltage                                                                                       | VLDO_1.0V                | setting by<br>reg_0x2B[2:1]=01<br>(default)              | -2.0% | 1.0 |       |      |

|                                                                                                      |                          | Setting by reg_0x2B[2:1]=10                              |       | 1.1 |       |      |

|                                                                                                      |                          | Setting by reg_0x2B[2:1]=11                              |       | 1.2 |       |      |

| Current Limit                                                                                        |                          |                                                          |       | 200 |       | mA   |

### **Electrical Characteristics (Continued)**

Limits apply over the full operating ambient temperature range (0°C  $\leq$  TA  $\leq$  85°C) and  $V_{INA} = V_{INB} = V_{INC} = V_{IN} = 5V$ , typical values are at  $T_A$ =25°C, unless otherwise specified.)

| Parameter                                           | Symbol                            | Conditions | Min  | Тур | Max  | Unit |  |  |  |

|-----------------------------------------------------|-----------------------------------|------------|------|-----|------|------|--|--|--|

| Logic Interface DC Electrical Specification         |                                   |            |      |     |      |      |  |  |  |

| Input Low Voltage<br>(PWR_GOOD, SDA, SCL,<br>VR_EN) | V <sub>IL</sub>                   |            | -0.3 |     | 0.3  | V    |  |  |  |

| Input High Voltage (SDA, SCL)                       | .,                                |            | 0.7  |     | 3.6  | V    |  |  |  |

| Input High Voltage<br>(PWR_GOOD, VR_EN)             | V <sub>IH</sub>                   |            | 1.26 |     | 3.6  | V    |  |  |  |

| Output Low Voltage (SDA, PWE_GOOD, GSI_n)           | V <sub>OL</sub>                   |            |      |     | 0.3  | V    |  |  |  |

| Output High Voltage (SDA)                           | V <sub>OH</sub>                   |            | 0.75 |     |      | V    |  |  |  |

| Output Low Current (SDA, PWR_GOOD, GSI_n)           | I <sub>OL</sub>                   |            |      |     | 3    | mA   |  |  |  |

| Output High Current (SDA)                           | I <sub>OH</sub>                   |            | -3   |     |      | mA   |  |  |  |

| Input Leakage Current                               | lu                                |            |      |     | ±5   | μΑ   |  |  |  |

| Output Leakage Current                              | I <sub>LO</sub>                   |            |      |     | ±5   | μA   |  |  |  |

| Rising Output Slew Rate (SDA)                       | 01                                |            | 0.1  |     | 1    | V/ns |  |  |  |

| Falling Output Slew Rate (SDA)                      | Slew rate                         |            | 0.1  |     | 3    | V/ns |  |  |  |

| I <sup>2</sup> C operate Frequency                  | f <sub>SCL,I</sub> <sup>2</sup> C |            | 0.01 |     | 1    | MHz  |  |  |  |

| I <sup>3</sup> C operate Frequency                  | f <sub>SCL,I</sub> <sup>3</sup> C |            | 0.01 |     | 12.5 | MHz  |  |  |  |

#### **Operation**

#### **PMIC Input Voltage Supply and Ramp Condition**

The FP9968 has one input supply from the platform: VIN Bulk.

The VIN\_Bulk supply is used by the PMIC for all three switch (SWA, SWB, SWC) output regulators and two LDO outputs (VOUT\_1.8V & VOUT\_1.0V) regulators. Note that the VOUT\_1.8V LDO output is separate and independent from SWC output, which is for the DRAM VPP rail. The VOUT\_1.0V LDO output is separate and independent from SWA or SWB.

At first power on, the VIN\_Bulk input supply shall reach a minimum threshold voltage of 4.25V before it can be detected as a valid input supply to the PMIC.

Once the VIN\_Bulk supply is valid and stable, the PMIC shall assert PWR\_GOOD output low, drive VOUT\_1.8V & VOUT\_1.0V supply within  $t_{1.8V\_Ready}$  and  $t_{1.0V\_Ready}$  time respectively. The PMIC drives PWR\_GOOD output signal low only when VIN\_Bulk input supply reaches minimum of 4.25V. The PWR\_GOOD output is pulled up to either 1.8V or 3.3V on the platform or on the host controller.

The PWR\_GOOD pull up voltage (either 1.8V or 3.3V) can be available before or after VIN\_Bulk is valid and stable. If PWR\_GOOD pull up voltage is available before VIN\_Bulk is applied, the PWR\_GOOD signal is High and remains High with no leakage path or damage to the PMIC. When VIN\_Bulk is applied to the PMIC, the PMIC asserts PWR GOOD output low.

The PMIC shall enable  $I^2C/I^3C$  bus interface function within  $t_{Management\_Ready}$ . The host shall not attempt to access the PMIC's memory registers until  $t_{Management\_Ready}$  timing requirement is satisfied.

#### **Power Up Initialization Sequence**

During power on, the host shall:

- [1] Ramp up VIN\_Bulk supply.

- [2] Hold VIN\_Bulk supply stable for a minimum of tVIN\_Bulk\_to\_VR\_Enable time.

- [3] Hold VR\_EN pin to static low or high.

- [4] During VIN\_Bulk ramp, if VR\_EN signal is held low, it can transition to high only once. Once high, it shall remain high. The VR\_EN signal is not allowed to transition to low during VIN\_Bulk ramp up.

- [5] If VR\_EN pin is held High during VIN\_Bulk ramp up or transitions to High during VIN\_Bulk ramp up, the PMIC turns on its output rails.

- [6] If VR\_EN pin is held Low during VIN\_Bulk Ramp, assert VR\_EN signal High to turn on PMIC output rails. Alternatively, host can issue VR Enable command by setting register 0x32[7] = 1 via I<sup>2</sup>C/I<sup>3</sup>C Basic bus or via DEVCTRL CCC to turn on PMIC output rails.

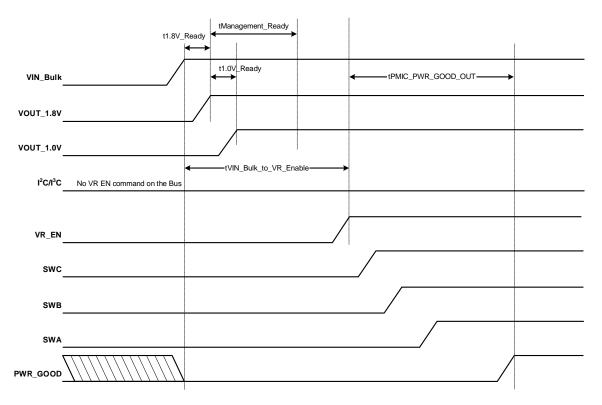

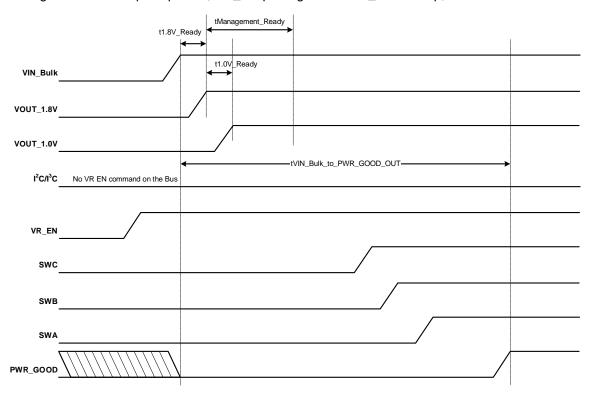

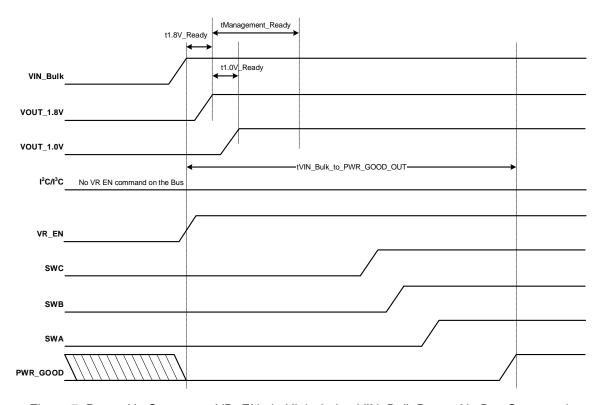

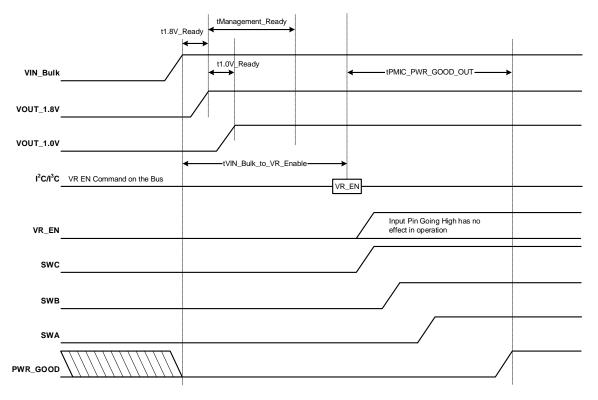

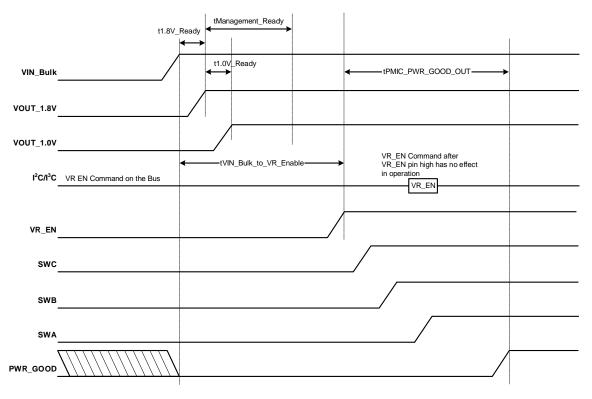

Figure 5 to Figure 9 shows example of PMIC power up initialization sequence. Note that the specific sequence of ramping the output regulators (SWA, SWB, SWC) is for example purpose only. The specific ramp up sequence is configurable through power on sequence configuration registers.

After VR Enable command is registered on the  $I^2C$  or  $I^3C$  Basic bus or VR\_EN pin is registered high, the PMIC shall complete the following steps within  $t_{\text{PMIC\_PWR\_GOOD\_OUT}}$ :

- [1] Check VIN\_Bulk Power Good status is valid.

- [2] Power up itself FP9968 executes Power On Sequence Config0 to Power On Sequence Config2 registers and configures FP9968 internal registers as programmed in DIMM vendor memory space registers.

- [3] Power up all enabled output switch regulators and ready for normal operation.

- [4] Update status registers 0x08[5,3:2] and floats PWR\_GOOD signal within maximum of  $t_{\text{PMIC\_PWR\_GOOD\_OUT}}$  time.

If PMIC PWR\_GOOD signal is not floated within  $t_{PMIC\_PWR\_GOOD\_OUT}$  time, the host can access the PMIC status registers for detailed information after  $t_{PMIC\_PWR\_GOOD\_OUT}$  time. The PMIC may NACK for any host request on I<sup>2</sup>C or I<sup>3</sup>C Basic bus after VR Enable command (either with VR\_EN pin high or on I<sup>2</sup>C/I<sup>3</sup>C Basic Bus) until  $t_{PMIC\_PWR\_GOOD\_OUT}$  time expires.

11

Figure 5. Power Up Sequence; VR\_EN pin High after VIN\_Bulk Ramp; No Bus Command

Figure 6. Power Up Sequence; VR\_EN pin High before VIN\_Bulk Ramp; No Bus Command

Figure 7. Power Up Sequence; VR\_EN pin High during VIN\_Bulk Ramp; No Bus Command

Figure 8. Power Up Sequence; With VR\_EN Bus Command

Figure 9. Power Up Sequence; With VR\_EN Pin

#### **Turn On Timing of PMIC Output Rail**

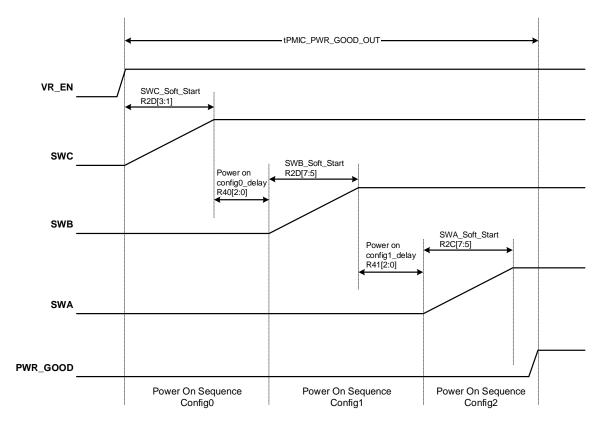

The Figure 10 below shows the timing relationship once the PMIC receives VR Enable command (either with VR\_EN pin or on I²C/I³C Basic bus) and when it floats PWR\_GOOD output signal; timing parameter tpmic\_pwR\_GOOD\_output signal; timing parameter is a sum of maximum soft start time and configured delay for each power on sequence configuration registers that are executed plus additional 5 ms timing margin error. The waveform shows each buck regulator output soft start time and delay time once the soft start time expires for each power on sequence config0 to power on sequence config2 registers. Note that if more than one regulators are enabled in a power on sequence config register and if those regulators have different soft start time programmed, then the larger value of that soft start time is used as a reference for delay timer to start. Each regulator will still follow different soft start time to turn on the buck regulator.

The specific example in Figure 10 uses three power on sequence config0 to config2 registers and only one buck regulator is enabled in each power on sequence config0 to config2 registers.

Figure 10. FP9968 Power On Timing

#### **Secure Mode& Programmable Mode of Operation**

Prior to issuing VR Enable command (either with VR\_EN pin or on I<sup>2</sup>C/I<sup>3</sup>C Basic bus), the host must configure the register 0x2F[2] appropriately as desired. The PMIC offers two modes of operation after VR Enable command (either with VR\_EN pin or on I<sup>2</sup>C/I<sup>3</sup>C Basic bus) is registered.

- [1] Programmable Mode In this mode, independent of when host issues VR Enable command (either with VR\_EN pin or on I<sup>2</sup>C/I<sup>3</sup>C Basic bus), the PMIC allows modification to any register in the host region as desired by the host and PMIC responds appropriately.

- [2] Secure Mode In this mode, after host issues VR Enable command (either with VR\_EN pin or on I<sup>2</sup>C/I<sup>3</sup>C Basic bus), the PMIC does not allow modification to registers 0x15 to 0x2F, register 0x32[7,5:0] in the host region as well as register 0x40 to 0x6F in the DIMM vendor region. These registers are written protected. Throughout this entire specification, when it refers to as PMIC allows access to the registers, it refers to write operation to the registers that are not write protected in secure mode or programmable mode. The host must power cycle the PMIC to make any modification. The PMIC power cycle is defined as complete removal of VIN\_Bulk input supply to the PMIC and this definition is applied to the entire specification. The Secure Mode is only applicable once VR Enable command (either with VR\_EN pin or on I<sup>2</sup>C/I<sup>3</sup>CBasic bus) is registered. This is important because by default register 0x2F[2] = 0 when PMIC is first powered up. Prior to VR Enable command (either with VR\_EN pin or on I<sup>2</sup>C/I<sup>3</sup>C Basic bus), PMIC allows modification to any registers in the host region.

#### **Power Down Output Regulators**

Regardless of how PMIC's output regulators are turned on (w/ VR\_EN pin or w/ VR Enable command on I<sup>2</sup>C/I<sup>3</sup>C Basic bus), the PMIC's output regulators are powered down as described below depending on PMIC's mode of operation.

#### Programmable Mode Operation; R1A[4] = 0

The PMIC allows host to power down any or all output regulators by any of the three methods below.

- [1] The VR Disable command (Register 0x32[7] = 0 or VR\_EN pin transitions to low). The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers. The PMIC controls the PWR\_GOOD signal as following in (a) and (b):

- (a) If VR Disable command with a pin (i.e. VR\_EN pin transitions to Low), PMIC asserts PWR\_GOOD signal Low. The host can re-enable the PMIC's output regulators by VR\_EN pin transition to High. The PMIC executes power on sequence config0 to config2 registers and floats PWR\_GOOD signal after tpmic\_pwr\_GOOD\_OUT timing parameter is satisfied.

- (b) If VR Disable command on a I<sup>2</sup>C/I<sup>3</sup>C Bus (i.e Register 0x32[7] = 0), PMIC keeps the PWR\_GOOD signal floating because this is an intentional command from the host and not a fault condition. The host can re-enable the PMIC's output regulators by issuing VR\_EN command on the I<sup>2</sup>C/I<sup>3</sup>C bus (i.e. Register 0x32[7] = 1). The PMIC executes power on sequence config0 to config2 registers and continues to float the PWR\_GOOD signal until t<sub>PMIC\_PWR\_GOOD\_OUT</sub> time at which point, PMIC assumes normal control of PWR GOOD signal.

- (c) The simultaneous usage of VR\_EN pin and I<sup>2</sup>C/I<sup>3</sup>C bus command to turn on/off the PMIC is not allowed. If the VR\_EN pin transitions to Low first, the PWR\_GOOD signal follows as described in (a) and PWR\_GOOD signal remains low even if there is a subsequent I<sup>2</sup>C/I<sup>3</sup>C bus command as described in (b).

- [2] Configuring one or more bits in register 0x2F[6,4:3] to '0' in any specific sequence that is desired by the host. The PMIC does not execute power off sequence config0 to config2 on its own. The PMIC keeps the PWR\_GOOD signal floating because this is intentional command from the host and not a fault condition. Note that host can re-enable any of disabled output regulators by

- configuring one or more bits in register 0x2F[6,4:3] to '1' in any specific sequence that is desired by the host. The PMIC keeps the PWR\_GOOD signal floating.

- [3] If register 0x32[5] = 1, driving PWR\_GOOD input low. The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers and drives PWR\_GOOD signal low. The PMIC preserves all register contents including the MTP error log registers. If host re-enables PMIC's output regulators by issuing VR\_EN command on the I<sup>2</sup>C/I<sup>3</sup>C Basic bus (i.e. register 0x32[7] = 1), the PMIC executes power on sequence config0 to config2 registers and floats PWR\_GOOD output signal after t<sub>PMIC\_PWR\_GOOD\_OUT</sub> timing parameter is satisfied. The PMIC does not require power cycle.

The PMIC, on its own, can generate internal VR Disable command at any time due to one or more events listed in "Trigger VR Disable".

The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers. The PMIC asserts PWR\_GOOD signal low. The host can re-enable PMIC's output regulators with VR Enable command with either register 0x32[7] = 1 or VR\_EN pin transitions to high and PMIC turns on its output regulators and floats PWR\_GOOD signal. The PMIC does not require power cycle.

#### Programmable Mode Operation; R1A[4] = 1

The PMIC allows host to power down any or all output regulators by any of the three methods below.

- [1] The VR Disable command (Register 0x32[7] = 0 or VR\_EN pin transitions to low). The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers and enters in P1 state. The PMIC controls the PWR\_GOOD signal as following in (a) and (b):

- (a) If VR Disable command with a pin (i.e. VR\_EN pin transitions to Low), PMIC asserts PWR\_GOOD signal Low. The host can re-enable the PMIC's output regulators by VR\_EN pin transition to High. The PMIC exits from P1 state and executes power on sequence config0 to config 2 registers and floats PWR\_GOOD signal after t<sub>PMIC\_PWR\_GOOD\_OUT</sub> timing parameter is satisfied.

- (b) If VR Disable command on a I<sup>2</sup>C/I<sup>3</sup>C Basic Bus (i.e Register 0x32[7] = 0), PMIC keeps the PWR\_GOOD signal floating because this is an intentional command from the host and not a fault condition. The PMIC exits from P1 state with only VR\_EN pin transition to High. The host can re-enable the PMIC's output regulators by VR\_EN pin transition to High and PMIC executes power on sequence config0 to config2 registers. The PMIC continues to float PWR\_GOOD signal until t<sub>PMIC\_PWR\_GOOD\_OUT</sub> timing parameter is satisfied and at that point PMIC assumes normal control of PWR\_GOOD signal.

- [2] Configuring one or more bits in register 0x2F[6,4:3] to 0 in any specific sequence that is desired by the host. The PMIC does not execute power off sequence config0 to config2 on its own. The PMIC keeps the PWR\_GOOD signal floating because this is intentional command from the host and not a fault condition. Note that host can re-enable any of disabled output regulators by configuring one or more bits in register 0x2F[6,4:3] to 1 in any specific sequence that is desired by the host. The PMIC keeps the PWR\_GOOD signal floating.

- [3] If register 0x32[5] = 1, driving PWR\_GOOD input low. The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers and drives PWR\_GOOD signal low. The PMIC preserves all register contents including the MTP error log registers. The PMIC does not enter in P1 state. If host re-enables PMIC's output regulators by issuing VR\_EN command on I<sup>2</sup>C/I<sup>3</sup>C Basic bus (i.e. Register 0x32[7] = 1), the PMIC executes power on sequence config0 to config2 registers and floats PWR\_GOOD signal after t<sub>PMIC\_PWR\_GOOD\_OUT</sub> timing parameter is satisfied. The PMIC does not require power cycle.

The PMIC, on its own, can generate internal VR Disable command at any time due to one or more events listed in "Trigger VR Disable". The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers. The PMIC does not enter in P1 state. The PMIC assert PWR\_GOOD signal low. The host can re-enable PMIC's output regulators with VR Enable command with either register 0x32[7] = 1 or VR\_EN pin transitions to high and PMIC turns on its output regulators and floats PWR\_GOOD signal. The PMIC does not require

power cycle.

#### Secure Mode Operation; R1A[4] = 0

The PMIC allows host to power down any or all output regulators by any of the two methods below.

- [1] The VR Disable command with VR EN pin transitions to low. The PMIC asserts PWR\_GOOD signal Low. The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers. The host can re-enable the PMIC's output regulators by VR EN pin transition to High. The PMIC executes power on sequence config0 to config2 registers and floats PWR GOOD signal after  $t_{\mbox{\scriptsize PMIC\_PWR\_GOOD\_OUT}}$  timing parameter is satisfied. Note that VR Disable or Enable command on  $I^2C/I^3C$  Basic Bus (i.e Register 0x32[7] = 0 or 1) has no effect on the PMIC. Also, configuring one or more bits in register 0x2F[6,4:3] to 0 has no effect on the PMIC.

- [2] If register 0x32[5] = 1, driving PWR GOOD input low. The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers; drives PWR GOOD signal low and unlocks only register 0x32 [7]. The PMIC preserves all register contents including the MTP error log registers and keeps all write protect registers locked except for the register 0x32[7]. When host issues VR Enable command by I<sup>2</sup>C/I<sup>3</sup>C Basic bus, the PMIC executes power on sequence config0 to config2 registers, floats PWR GOOD output signal after t<sub>PMIC\_PWR\_GOOD\_OUT</sub> timing parameter is satisfied and re-locks register 0x32[7]. The PMIC does not require power cycle to re-enable PMIC's output regulators.

The PMIC, on its own, can generate internal VR Disable command at any time due to one or more events listed in "Trigger VR Disable". The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers. The PMIC assert PWR\_GOOD signal low. The PMIC requires power cycle. The VR Enable command with either register 0x32[7] = 1 or VR\_EN pin transitions to high has no effect on PMIC and PMIC keeps it PWR\_GOOD signal low.

#### Secure Mode Operation; R1A[4] = 1

The PMIC allows host to power down any or all output regulators by any of the two methods below.

- [1] The VR Disable command with VR EN pin low. The **PMIC** transitions to asserts PWR\_GOOD signal Low. The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers and enters in P1 state. The host can re-enable the PMIC's output regulators by VR EN pin transition to High. The PMIC exits from P1 state and execute power on sequence config0 to config2 registers and floats PWR\_GOOD signal after t\_PMIC\_PWR\_GOOD\_OUT timing parameter is satisfied. Note that VR Disable or Enable command on a I<sup>2</sup>C/I<sup>3</sup>C Basic Bus (i.e Register 0x32[7] = 0 or 1) has no effect on the PMIC. Also, configuring one or more bits in register 0x2F[6,4:3] to 0 has no effect on the PMIC.

- [2] If register 0x32[5] = 1, driving PWR\_GOOD input low. The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers; drives PWR\_GOOD signal low and unlocks only register 0x32[7]. The PMIC preserves all register contents including the MTP error log registers and keeps all write protect registers locked except for the register 0x32[7]. The PMIC does not enter in P1 state. When host issues VR Enable command by I<sup>2</sup>C/I<sup>3</sup>C Basic bus, the PMIC executes Power on sequence config0 to config2 registers, floats PWR GOOD output signal after t<sub>PMIC PWR GOOD OUT</sub> timing parameter is satisfied and re-locks register 0x32[7]. The PMIC does not require power cycle to re-enable PMIC's output regulators.

The PMIC, on its own, can generate internal VR Disable command at any time due to one or more events listed in "Trigger VR Disable". The PMIC executes power off sequence config0 to config2 to preserve the appropriate voltage relationship as configured in the registers. The PMIC does not enter in P1 state. The PMIC assert PWR\_GOOD signal low. The PMIC requires power cycle. The VR Enable command with either register 0x32[7] = 1 or VR\_EN pin transitions to high has no effect on PMIC and PMIC keeps it PWR\_GOOD signal low.

#### **Turn Off Timing of PMIC Output Rail**

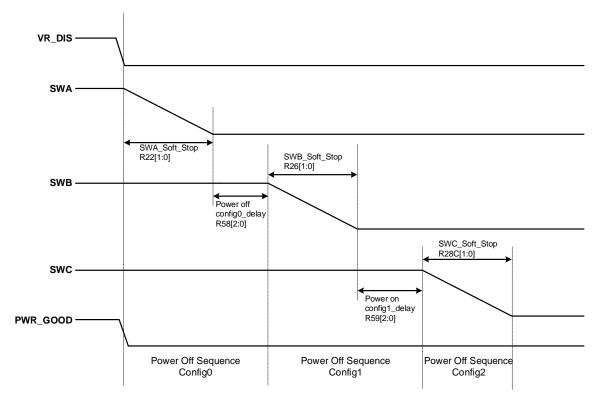

The Figure 11 below shows the timing relationship once the PMIC registers VR Disable command internally due to fault condition as listed in "Events Interrupt Summary". The waveform shows each buck regulator output soft stop time and delay time once the soft stop time expires from each power off sequence config0 to config2 registers. Note that if more than one regulators are disabled in a power off sequence config register and if those regulators have different soft stop time programmed, then the larger value of that soft stop time is used as a reference for delay timer to start. Each regulator will still follow different soft stop time to turn off the buck regulator.

The specific example in Figure 11 uses only three power off sequence config0 to config2 registers and only one buck regulator is disabled in power off sequence config0, config1 and config2 registers.

Figure 11. FP9968 Power Off Timing

#### Idle State and Quiescent Power State

Quiescent Power State definition: VIN\_Bulk nominal = 5.0 V. All circuits including PMIC switch output and LDO output regulators are off. VR\_EN signal is at static low or high level.  $I^2C$  or  $I^3C$  Basic interface access is not allowed and is pulled high. PID signal is at static low or high level. This state is only applicable if register 0x1A[4] = 1. This state is labeled as P1 state in Table 1 below.

Idle Power State definition: VIN\_Bulk nominal = 5.0 V. All circuits including PMIC switch output and LDO output regulators are on with 0A load. VR\_EN signal is at static low or high level.  $I^2C$  or  $I^3C$  Basic interface access is allowed but bus is pulled high. PID signal is at static low or high level. This state is only applicable if register 0x1A[4] = 0. This state is a same state as P3 state but load on all switch outputs regulators and LDO output regulators is 0 A.

| Table 1. High Level Finite State Description | วท |

|----------------------------------------------|----|

|----------------------------------------------|----|

| State                                             | Description                                                                                                                                                            |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0                                                | 1. VIN_Bulk invalid                                                                                                                                                    |

| P1                                                | 1. R1A[4] = 1 2. Entry from P3 State Only                                                                                                                              |

| P2_A1 (Non-Fault Event)                           | <ol> <li>All registers are readable. All non-protect registers are writable.</li> <li>All enabled output rails are active.</li> <li>PWR_GOOD is high.</li> </ol>       |

| P2_A2 (Fault Event)                               | 1. Transition from P3; After VR Enable Command 2. All Switch Regulators are Off 3. All LDOs are ON 4. PWR_GOOD Output = L 5. VR_EN Input = L or H 6. R32[7] = 0        |

| P2_B                                              | 1. Transient from P0 or P1 State; Before VR Enable Command 2. All Switch Regulators are Off 3. All LDOs are on 4. PWR_GOOD Output = L 5. VR_EN Input = L 6. R32[7] = 0 |

| P3 (Regulation Mode or<br>Bulk Link Monitor Mode) | All Switch Regulators are On     R32[7] = 1                                                                                                                            |

### GSI\_n Signal

General Status Interrupt (GSI\_n) is an Open Drain output signal. By default at power on, GSI\_n output is disabled. The host can enable the GSI\_n output by setting register 0x1B[3] = 1. Typically, GSI\_n output is pulled up to  $10K\Omega$  resistor to 1.8 V or 3.3 V. The PMIC asserts GSI\_n output for the events as described in Table 2.

### Function Interrupt - PWR\_GOOD and GSI\_n Output Signals

This section defined the output functionality of GSI\_n pin and PWR\_GOOD pin.

When mask register bits are not set, the PMIC asserts its GSI\_n output and assert PWR\_GOOD output signals as shown in Table 2 when any event occurs. The table also highlights the events that cause PMIC to generate internally VR Disable command. For remaining events that does not trigger internal VR Disable command, the PMIC continues to operate as normal.

### **Function Interrupt (Continued)**

Table 2. Events Interrupt Summary

| Event                          | Status<br>Bit | Clear<br>Bit | Mask<br>Bit | Threshold<br>Bits     | Trigger VR<br>Disable? | PWR_GOOD<br>Output | GSI_n |

|--------------------------------|---------------|--------------|-------------|-----------------------|------------------------|--------------------|-------|

| VIN_Bulk Over Voltage          | R08[0]        | R10[0]       | R15[0]      | R1B[7]                | Yes                    | Low                | Low   |

| SWA Output Power Good          | R08[5]        | R10[5]       | R15[5]      | R22[5:4],<br>R22[3:2] | No                     | Low                | Low   |

| SWB Output Power Good          | R08[3]        | R10[3]       | R15[3]      | R26[5:4],<br>R26[3:2] | No                     | Low                | Low   |

| SWC Output Power Good          | R08[2]        | R10[2]       | R15[2]      | R28[5:4],<br>R28[3:2] | No                     | Low                | Low   |

| 1.8V LDO Power Good            | R09[5]        | R11[5]       | R16[5]      | R1A[2]                | No                     | Low                | Low   |

| 1.0V LDO Power Good            | R33[2]        | R14[2]       | R19[2]      | R1A[0]                | No                     | Low                | Low   |

| SWA Output Over Voltage        | R0A[7]        | R12[7]       | R17[7]      | R22[5:4]              | Yes                    | Low                | Low   |

| SWB Output Over Voltage        | R0A[5]        | R12[5]       | R17[5]      | R26[5:4]              | Yes                    | Low                | Low   |

| SWC Output Over Voltage        | R0A[4]        | R12[4]       | R17[4]      | R28[5:4]              | Yes                    | Low                | Low   |

| SWA Output Under Voltage       | R0B[3]        | R13[3]       | R18[3]      | R22[3:2]              | Yes                    | Low                | Low   |

| SWB Output Under Voltage       | R0B[1]        | R13[1]       | R18[1]      | R26[3:2]              | Yes                    | Low                | Low   |

| SWC Output Under Voltage       | R0B[0]        | R13[0]       | R18[0]      | R28[3:2]              | Yes                    | Low                | Low   |

| SWA Output Current Limit       | R0B[7]        | R13[7]       | R18[7]      | R20[7:6]              | No                     | High               | Low   |

| SWB Output Current Limit       | R0B[5]        | R13[5]       | R18[5]      | R20[3:2]              | No                     | High               | Low   |

| SWC Output Current Limit       | R0B[4]        | R13[4]       | R18[4]      | R20[1:0]              | No                     | High               | Low   |

| SWA Output High Current /Power | R09[3]        | R11[3]       | R16[3]      | R20[7:6]              | No                     | High               | Low   |

| SWB Output High Current /Power | R09[1]        | R11[1]       | R16[1]      | R20[3:2]              | No                     | High               | Low   |

| SWC Output High Current /Power | R09[0]        | R11[0]       | R16[0]      | R20[1:0]              | No                     | High               | Low   |

| High Temperature Warning       | R09[7]        | R11[7]       | R16[7]      | R1B[2:0]              | No                     | High               | Low   |

| Critical Temperature           | R08[6]        | N/A          | N/A         | R2E[2:0]              | Yes                    | Low                | Low   |

| PEC Error                      | R0A[3]        | R12[3]       | R17[3]      | N/A                   | No                     | High               | Low   |

| Parity Error                   | R0A[2]        | R12[2]       | R17[2]      | N/A                   | No                     | High               | Low   |

The host is expected to read appropriate status registers to determine and isolate the cause of the GSI\_n signal assertion or PWR\_GOOD signal assertion. The host may attempt to clear or mask the appropriate corresponding interrupt event. The PMIC keeps the GSI\_n signal asserted or PWR\_GOOD signal asserted until the appropriate corresponding registers are explicitly cleared or masked by the host. Table 3 and Table 4 shows the PMIC's response of GSI\_n signal and PWR\_GOOD output signal for each event before and after host issues the Clear command. The Table 3 and Table 4 assumes that all mask bits are either '0' or '1' for simplicity.

# **Function Interrupt (Continued)**

Table 3. FP9968 Response for Clear Command by Host 1

|                                   | Event Occurred; All Mask Bits = '0' |                 | Clear Command;<br>Event Not Present; |                                                       | Event Occurred; All<br>Mask Bits = '1' |                 | Clear Command;<br>Event Not Present; |                                      |  |

|-----------------------------------|-------------------------------------|-----------------|--------------------------------------|-------------------------------------------------------|----------------------------------------|-----------------|--------------------------------------|--------------------------------------|--|

| Event                             | Musik Bi                            | Mask Bits = 0   |                                      | All Mask Bits = '0'  R2F[1:0] = "00" or  "01" or "10" |                                        | R2F[1:0] = "00" |                                      | All Mask Bits = '1'  R2F[1:0] = "00" |  |

|                                   | PWR_GOOD<br>Output                  | GSI_n<br>Output | PWR_GOOD<br>Output                   | GSI_n<br>Output                                       | PWR_GOOD<br>Output                     | GSI_n<br>Output | PWR_GOOD<br>Output                   | GSI_n<br>Output                      |  |

| VIN_Bulk Over Voltage             | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWA Output Power Good             | Low                                 | Low             | High                                 | High                                                  | Low                                    | High            | High                                 | High                                 |  |

| SWB Output Power Good             | Low                                 | Low             | High                                 | High                                                  | Low                                    | High            | High                                 | High                                 |  |

| SWC Output Power Good             | Low                                 | Low             | High                                 | High                                                  | Low                                    | High            | High                                 | High                                 |  |

| 1.8V LDO Power Good               | Low                                 | Low             | High                                 | High                                                  | Low                                    | High            | High                                 | High                                 |  |

| 1.0V LDO Power Good               | Low                                 | Low             | High                                 | High                                                  | Low                                    | High            | High                                 | High                                 |  |

| SWA Output Over Voltage           | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWB Output Over Voltage           | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWC Output Over Voltage           | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWA Output Under Voltage          | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWB Output Under Voltage          | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWC Output Under Voltage          | Low                                 | Low             | Low                                  | High                                                  | Low                                    | High            | Low                                  | High                                 |  |

| SWA Output Current Limit          | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| SWB Output Current Limit          | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| SWC Output Current Limit          | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| SWA Output High Current /Power    | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| SWB Output High Current /Power    | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| SWC Output High Current<br>/Power | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| High Temperature Warning          | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| Critical Temperature              | Low                                 | Low             | Power<br>Cycle                       | Power<br>Cycle                                        | Low                                    | Low             | Power<br>Cycle                       | Power<br>Cycle                       |  |

| PEC Error                         | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

| Parity Error                      | High                                | Low             | High                                 | High                                                  | High                                   | High            | High                                 | High                                 |  |

## **Function Interrupt (Continued)**

Table 4. FP9968 Response for Clear Command by Host 2

| Event                                     | Event Occurred; All<br>Mask Bits = '1' |        | Clear Command;<br>Event Not Present;<br>All Mask Bits = '1' |                | Event Occurred; All<br>Mask Bits = '1' |        | Clear Command;<br>Event Not Present;<br>All Mask Bits = '1' |                |

|-------------------------------------------|----------------------------------------|--------|-------------------------------------------------------------|----------------|----------------------------------------|--------|-------------------------------------------------------------|----------------|

| 2.0                                       | R2F[1:0] = "01"                        |        | R2F[1:0] = "01"                                             |                | R2F[1:0] = "10"                        |        | R2F[1:0] = "10"                                             |                |

|                                           | PWR_GOOD                               | _      | PWR_GOOD                                                    | GSI_n          | PWR_GOOD                               | GSI_n  | PWR_GOOD                                                    | GSI_n          |

| \/\b\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ | Output                                 | Output | Output                                                      | Output         | Output                                 | Output | Output                                                      | Output         |

| VIN_BULK Over Voltage                     | Low                                    | Low    | Low                                                         | High           | Low                                    | High   | Low                                                         | High           |

| SWA Output Power Good                     | High                                   | Low    | High                                                        | High           | High                                   | High   | High                                                        | High           |

| SWB Output Power Good                     | High                                   | Low    | High                                                        | High           | High                                   | High   | High                                                        | High           |

| SWC Output Power Good                     | High                                   | Low    | High                                                        | High           | High                                   | High   | High                                                        | High           |

| 1.8V LDO Power Good                       | High                                   | Low    | High                                                        | High           | High                                   | High   | High                                                        | High           |

| 1.0V LDO Power Good                       | High                                   | Low    | High                                                        | High           | High                                   | High   | High                                                        | High           |

| SWA Output Over Voltage                   | Low                                    | Low    | Low                                                         | High           | Low                                    | High   | Low                                                         | High           |

| SWB Output Over Voltage                   | Low                                    | Low    | Low                                                         | High           | Low                                    | High   | Low                                                         | High           |

| SWC Output Over Voltage                   | Low                                    | Low    | Low                                                         | High           | Low                                    | High   | Low                                                         | High           |

| SWA Output Under Voltage                  | Low                                    | Low    | Low                                                         | High           | Low                                    | High   | Low                                                         | High           |